## 逻辑门 Logic Gate

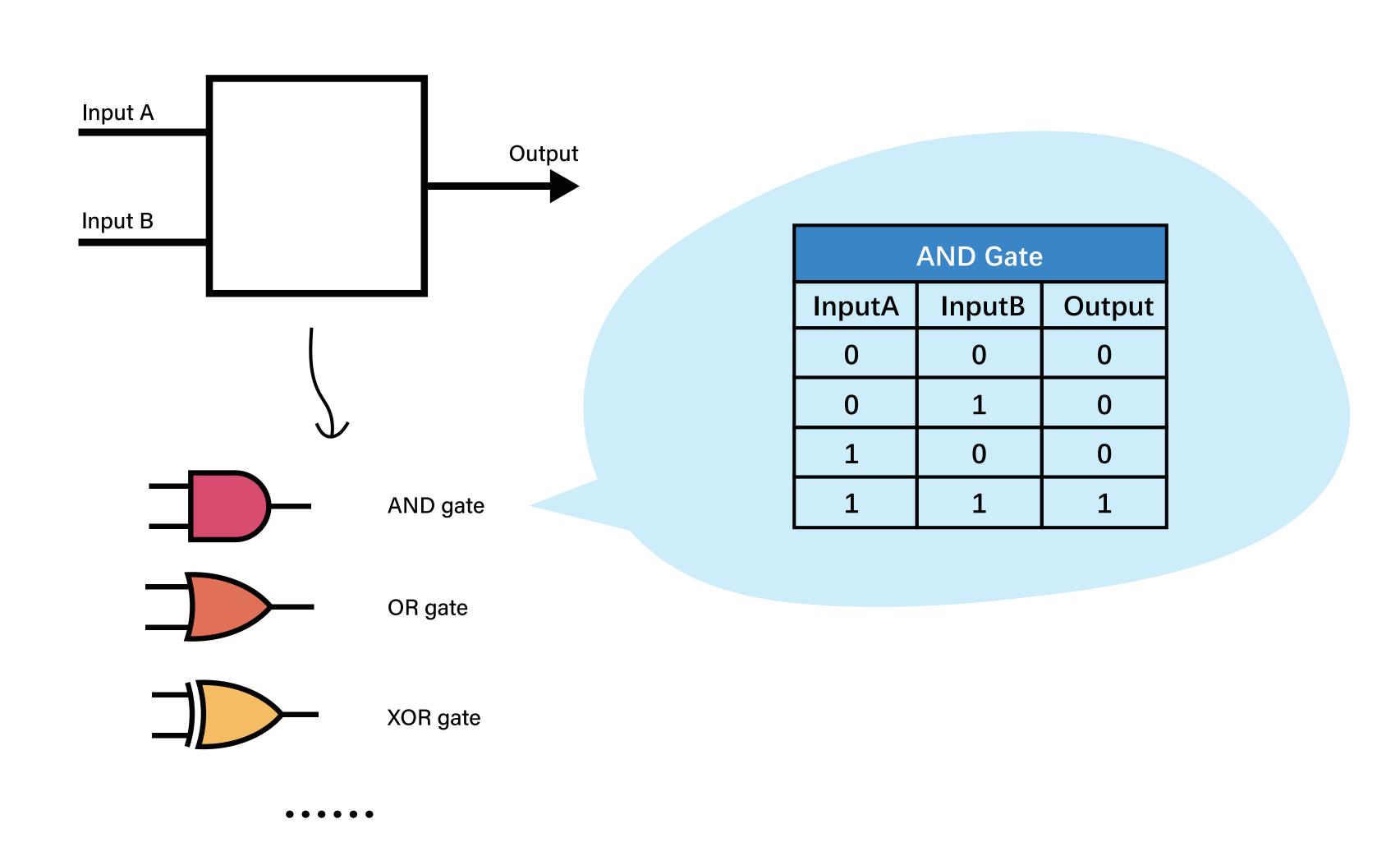

首先我们尝试解释逻辑门的概念。逻辑门是数字电路的基本构建块。大多数逻辑门有两个输入和一个输出。在任何给定时刻,每个终端处于两个二进制条件之一,低(0)或高(1),由不同的电压电平表示。

A logic gate is an elementary building block of a digital circuit. Most logic gates have two inputs and one output. At any given moment, every terminal is in one of the two binary conditions, low (0) or high (1), represented by different voltage levels.

| AND Gate |        |        |  |  |

|----------|--------|--------|--|--|

| InputA   | InputB | Output |  |  |

| 0        | 0      | 0      |  |  |

| 0        | 1      | 0      |  |  |

| 1        | 0      | 0      |  |  |

| 1        | 1      | 1      |  |  |

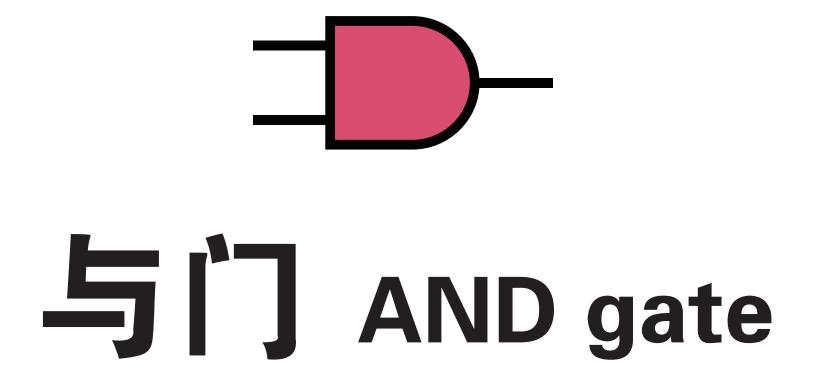

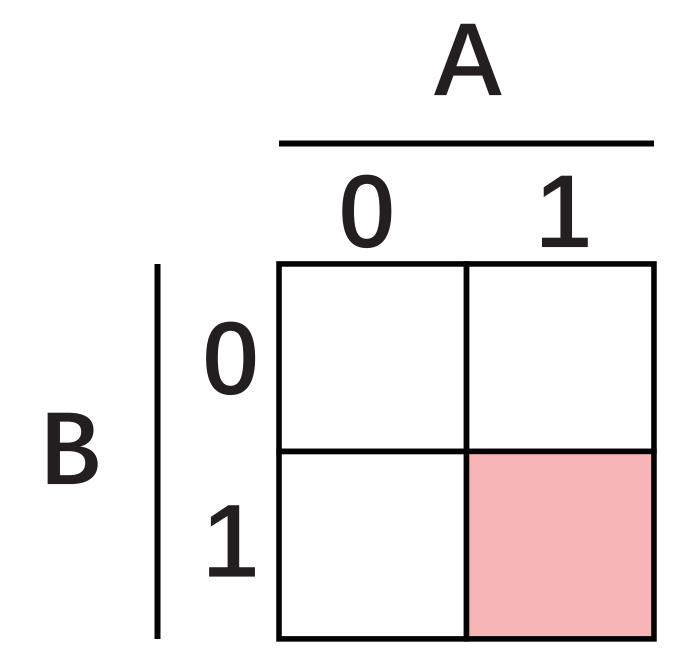

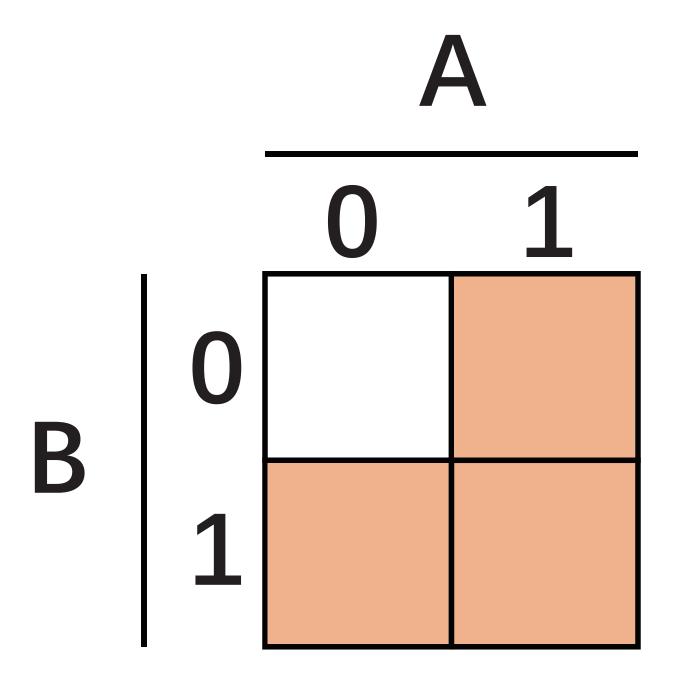

与门,又称"与电路"、逻辑"与"电路。是执行"与"运算的基本逻辑门电路。有两个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

The AND gate, also known as the "AND circuit", the logic "AND" circuit. It is the basic logic gate that performs the AND operation. There are two inputs and one output. The output is high when all inputs are high (logic 1) at the same time, otherwise the output is low (logic 0).

| OR Gate |        |        |  |  |

|---------|--------|--------|--|--|

| InputA  | InputB | Output |  |  |

| 0       | 0      | 0      |  |  |

| 0       | 1      | 1      |  |  |

| 1       | 0      | 1      |  |  |

| 1       | 1      | 1      |  |  |

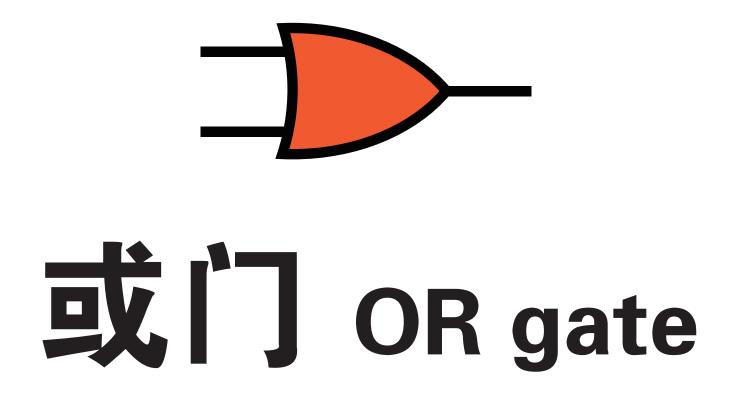

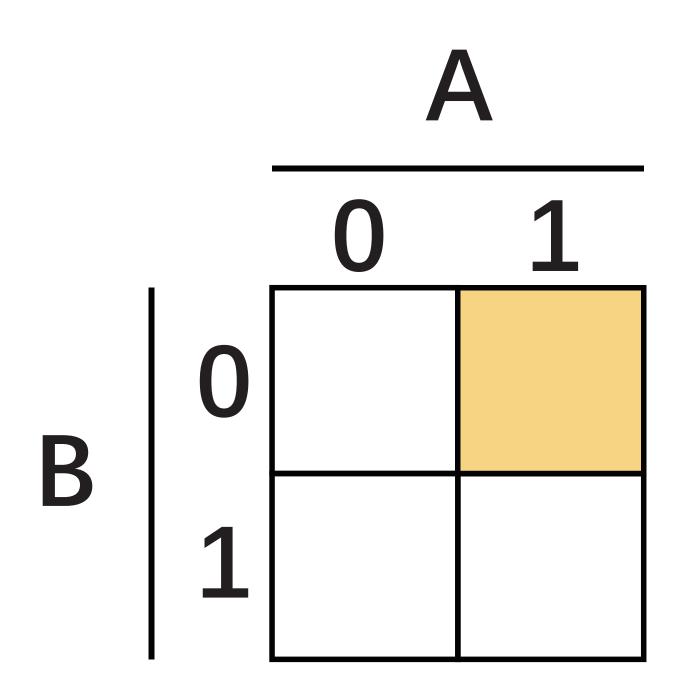

或门,又称"或电路"。如果几个条件中,只要有一个条件得到满足,某事件就会发生,这种关系叫做"或"逻辑关系。或门有两个输入端,一个输出端,只要输入中有一个为高电平时(逻辑"1"),输出就为高电平(逻辑"1");只有当所有的输入全为低电平(逻辑"0")时,输出才为低电平(逻辑"0")。

The OR gates, also known as "OR circuits". The OR gate has two inputs and one output. As long as one of the inputs is high (logic "1"), the output is high (logic "1"); only when all inputs are low (logic "0"), the output is low (logic "0").

## NIMPLY Gate

| A NIMPLY B |        |        |  |  |

|------------|--------|--------|--|--|

| InputA     | InputB | Output |  |  |

| 0          | 0      | 0      |  |  |

| 0          | 1      | 0      |  |  |

| 1          | 0      | 1      |  |  |

| 1          | 1      | 0      |  |  |

NIMPLY Gate是一种较为少见的逻辑门。NIMPLY Gate有两个输入端,一个输出端。当且仅当A输入为高电平(逻辑"1")而B输入为低电平(逻辑"0")时,输出才为高电平(逻辑"1")。虽然这个逻辑门在日常生活中不常见,但是在生物领域却有很重要的应用。

The NIMPLY Gate is a relatively rare logic gate. The NIMPLY Gate has two inputs and one output. The output is high (logic "1") if and only if the A input is high (logic "1") and the B input is low (logic "0"). Although this logic gate is not common in daily life, it has important applications in the biological field.

## Notch蛋白 NotchProtein

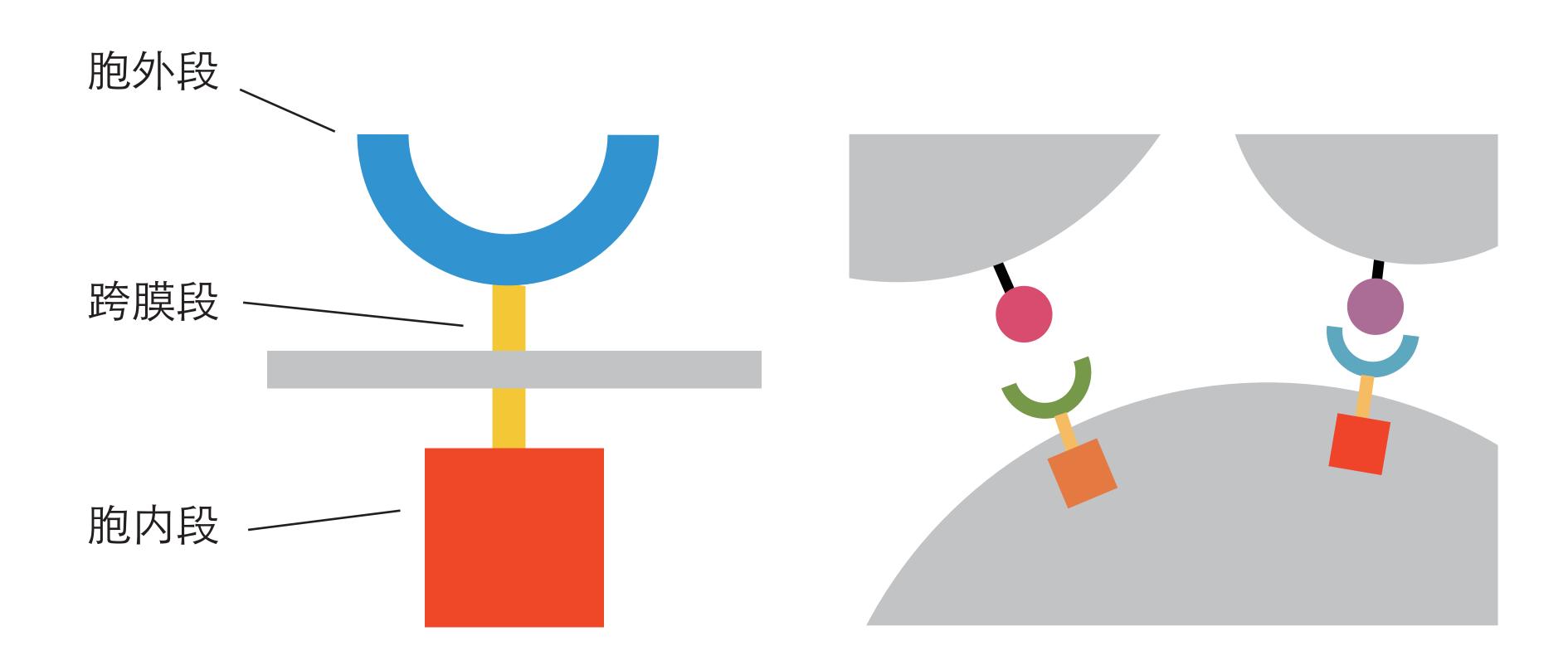

Notch蛋白是一个位于细胞膜上的蛋白,由胞外段、胞内段和跨膜段组成。Notch的胞外段介导与配体的相互作用,胞内段可以进入细胞核充当转录激活因子。

The Notch protein is a protein located on the cell membrane and consists of an extracellular segment, an intracellular segment, and a transmembrane segment. The Notch extracellular domain (NECD) mediates interaction with a ligand, and the intracellular domain (NICD) can enter the necleus and act as a transcriptional activator.

## 与门的实现 Implementation of

**AND Gate**

| AND Gate |        |        |  |  |

|----------|--------|--------|--|--|

| InputA   | InputB | Output |  |  |

| 0        | 0      | 0      |  |  |

| 0        | 1      | 0      |  |  |

| 1        | 0      | 0      |  |  |

| 1        | 1      | 1      |  |  |

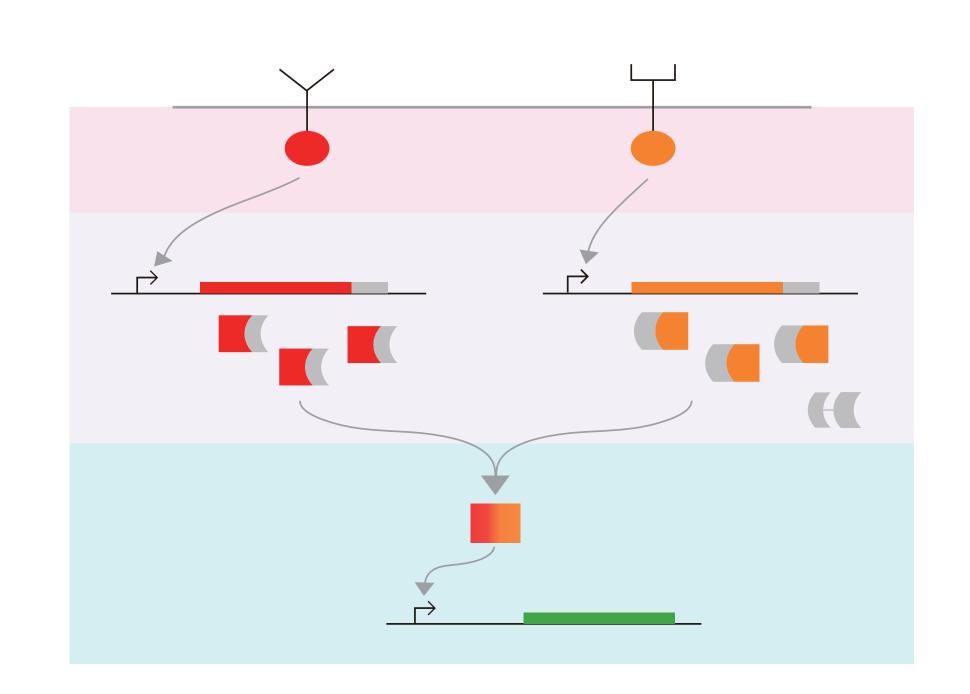

与门的实现中我们使用了两个notch蛋白,分别对应两个不同的转录因子。两个转录因子进入细胞核后分别通过一次转录激活作用,起到信号放大的效果,进而引起下游信号蛋白的表达。两个信号蛋白分别带有一段内含肽序列。当两者同时存在时,即发生内含肽的剪切过程,形成一个新的转录因子蛋白,激活报告基因的表达。

In the implementation of the AND gate we used two notch proteins, corresponding to two different transcription factors. Two transcription factors enter the nucleus and acitvate transcription, which acts as signal amplification. It in turn causes the expression of downstream signaling proteins. The two signaling proteins carry an intein sequence, respectively. When both proteins are present, the intrinsic peptide cleavage process occurs to form a new transcription factor protein, which then activates the expression of the reporter gene.